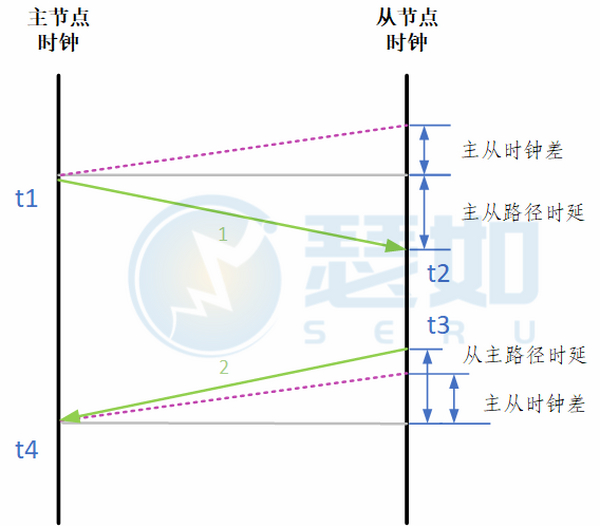

瑟如TDC可以达到20ps的时间戳精度,在此基础上实现的双向时间比对也可达到优于50ps的比对精度。《采用瑟如TDC实现高精度双向时间同步》将以连载的形式,用5篇左右的篇幅从多方面介绍双向时间比对的基本原理、实验设置、实验结果分析以及实现过程中一些Vivado、SDK、LwIP的一些技术细节。本篇是改系列的第一篇,介绍双向时间比对的基本原理。

查看更多使用该译码IP,可在PL侧直接得到解码后的时间戳数据。利用FPGA PL端强大的自定义能力,用户可以开发高度并行化的模块,甚至利用深度学习单元DPU对TDC IP产生的大量实时测量数据进行数据处理,从而实现低延迟的环境感知算法。

查看更多瑟如电子优化TDC读出机制,在Kintex开发板KC705上实现了每通道高达160MHz的Hit Rate,极大地拓展了SeruTek TDC的使用场景。

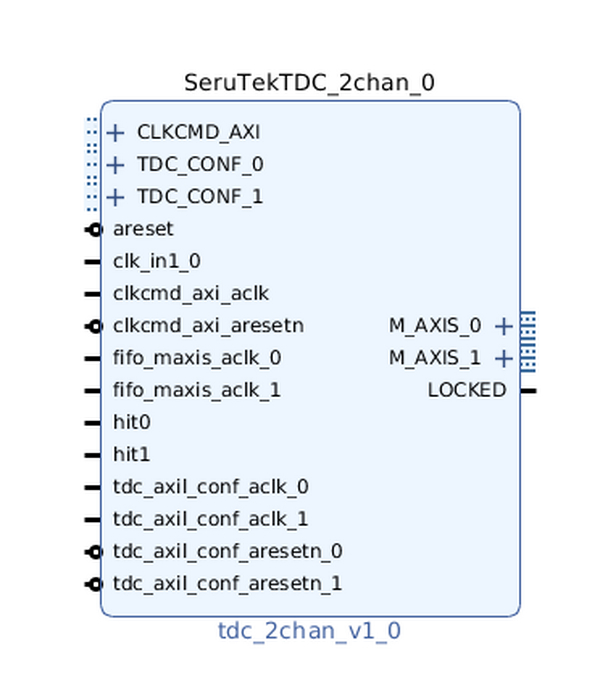

查看更多为了便于客户测试评估,瑟如电子现提供基于zynq(7020及以下)的评估版双通道TDC IP核。该IP核基于加密网表封装,并采用标准 AXI-lite、AXI-Stream接口,可方便地在Vivado 可视化设计环境中使用。 免费供评估的IP核是全功能IP核,hit信号频率可高达70MHz,IP核内集成FIFO可供每通道最大速率测量2048个测试点(连续测量速率受限于IP核外的数据读出速率,通过使用DMA等技术可以轻易达到30Msa/s的连续测量速度),测时量程为70年。

查看更多2019年10月,瑟如电子科技发布了基于Xilinx 7系列 FPGA的TDC产品:SeRuTDC。具有测量精度高,量程广,多通道集成度高,数据吞吐量大等优点。当在Zynq SoC上实现时,更能提供TDC测量,采集,处理及分析的一体化解决方案。相比采用ASIC的TDC方案,能够大幅降低开发周期和费用,并提供大量程、多通道、大数据吞吐量等ASIC方案很难实现的特性。

查看更多最新动态

-

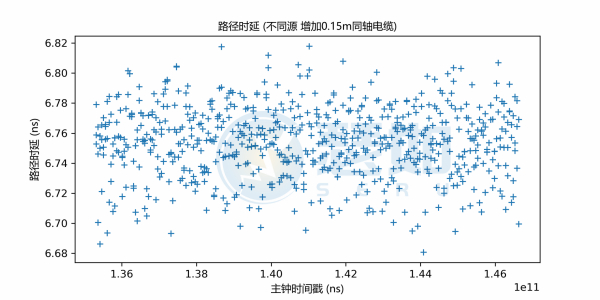

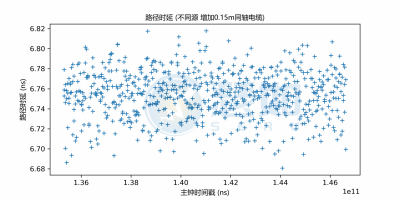

采用瑟如TDC实现高精度双向时间比对(四)--测试结果分析

2019-11-02 -

采用瑟如TDC实现高精度双向时间比对(三)--实验数据

2019-11-01 -

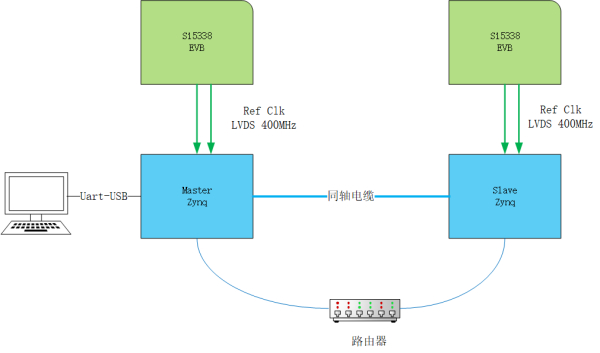

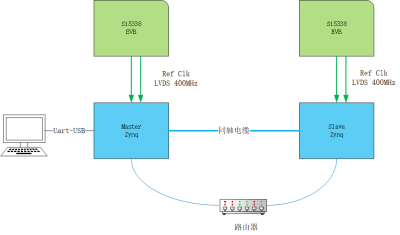

采用瑟如TDC实现高精度双向时间比对(二)--实验设置

2019-11-01 -

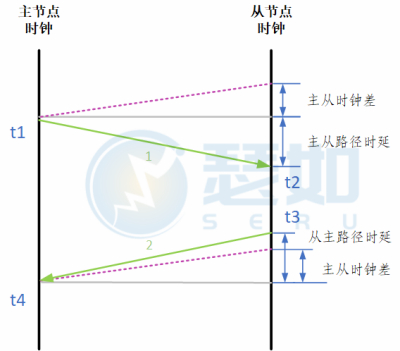

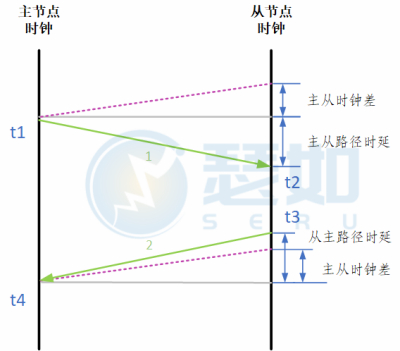

采用瑟如TDC实现高精度双向时间比对(一)-- 基本原理

2019-11-01 -

TDC PL侧译码单元准备就绪!

2020-11-16